# Impact of Gate Insulation Material and Thickness on Pocket Implanted MOS Device

Muhibul Haque Bhuyan

Abstract—This paper reports on the impact study with the variation of the gate insulation material and thickness on different models of pocket implanted sub-100 nm n-MOS device. The gate materials used here are silicon dioxide (SiO2), aluminum silicate (Al<sub>2</sub>SiO<sub>5</sub>), silicon nitride (Si<sub>3</sub>N<sub>4</sub>), alumina (Al<sub>2</sub>O<sub>3</sub>), hafnium silicate (HfSiO<sub>4</sub>), tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>), hafnium dioxide (HfO<sub>2</sub>), zirconium dioxide (ZrO2), and lanthanum oxide (La2O3) upon a ptype silicon substrate material. The gate insulation thickness was varied from 2.0 nm to 3.5 nm for a 50 nm channel length pocket implanted n-MOSFET. There are several models available for this device. We have studied and simulated threshold voltage model incorporating drain and substrate bias effects, surface potential, inversion layer charge, pinch-off voltage, effective electric field, inversion layer mobility, and subthreshold drain current models based on two linear symmetric pocket doping profiles. We have changed the values of the two parameters, viz. gate insulation material and thickness gradually fixing the other parameter at their typical values. Then we compared and analyzed the simulation results. This study would be helpful for the nano-scaled MOS device designers for various applications to predict the device behavior.

**Keywords**—Linear symmetric pocket profile, pocket implanted n-MOS Device, model, impact of gate material, insulator thickness.

# I. Introduction

THE long-channel conventional bulk MOS devices have I homogeneous doping concentration and accordingly the threshold voltage model was derived for them [1]. However, as the channel length of such devices was downsized to deepsub-micrometer or beyond the 100 nm regime, Short-Channel Effects (SCE) started to arise. For the short-channel bulk MOS devices, the SCE includes the threshold voltage reduction, augmented leakage current during off-state, and punch through the bulk [2]. The SCEs are witnessed due to the 2-D nature of the surface potential and higher electric fields along the device channel. To combat these effects, horizontal channel doping engineering exploiting halo/pocket implant near the source and drain regions was found very useful, and as such corresponding MOS models for various parameters were developed [3]-[7]. If the doping concentration becomes non-homogeneous along the channel then it experiences the opposite effect on the threshold voltage called the Reverse Short-Channel Effect (RSCE) [8] that can annul the SCE of the MOS device [9]. In several earlier works of pocket implanted MOSFET modeling, it was shown that those models are capable of describing the behavior of the pocket implanted

M. H. Bhuyan is with the Department of Electrical and Electronic Engineering (EEE), Southeast University, 251/1 & 252 Tejgaon Industrial cum Commercial Area, Dhaka 1208, Bangladesh (phone: 88-01815-657346; e-mail: muhibulhb@gmail.com).

MOSFET for the channel length up to 50 nm [10], [11]. Those models incorporated several shapes of pocket profiles, like linear [12], Gaussian [13], and hyperbolic cosine [14] profiles. It was shown that the linear profile also works very well taking less simulation time [12]. However, as the channel length goes down, we have to reduce the gate insulation thickness and increase the gate dielectric constant to avoid threshold voltage lowering further and hence to improve the device performance parameters. It has already been established that by increasing the dielectric strength that is using high-k dielectric materials or by decreasing the gate insulation layer thickness, we can improve the performances of the conventional and advanced MOS devices [15]-[19]. However, this study was not extended to the pocket implanted nano-scaled devices. Therefore, in this work, we have studied various models of the pocket implanted MOS devices by changing the gate insulation materials and gate insulation layer thickness and analyzed their impacts on the device performance in the nano-scaled regime.

## II. POCKET DOPED MOS DEVICE STRUCTURE

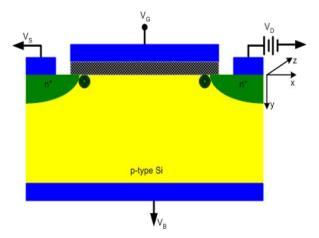

The pocket embedded n-MOS device construction is shown in Fig. 1. The presumed co-ordinate scheme is presented at the right-hand part of the device construction.

Fig. 1 Pocket embedded n-MOS construction with symmetric pockets both at the source and drain wings [21]

Table I shows all the device dimensions and parameters along with their symbols, values, and units used in this work. The device dimensions are measured according to the coordinate system of Fig. 1.

TABLE I

DEVICE DIMENSIONS AND DEVICE QUANTITIES [10]

| DEVICE DIMENSIONS MAD DEVICE QUANTITIES [10]          |                      |                      |                  |  |

|-------------------------------------------------------|----------------------|----------------------|------------------|--|

| Device Dimension/Quantity                             | Symbol               | Value                | Unit             |  |

| p-Si substrate doping concentration                   | $N_{sub}$            | $4.2 \times 10^{17}$ | cm <sup>-3</sup> |  |

| Peak pocket doping concentration at source/drain side | $N_{sub}$            | $1.5 \times 10^{18}$ | cm <sup>-3</sup> |  |

| Source or drain doping concentration                  | $N_{sd}$             | $9.0 \times 10^{20}$ | cm <sup>-3</sup> |  |

| Channel length                                        | L                    | 50                   | nm               |  |

| Pocket length                                         | $L_p$                | 20-30                | nm               |  |

| Junction depth                                        | $r_{j}$              | 25                   | nm               |  |

| Insulator thickness                                   | $t_{ox}$             | 2-3.5                | nm               |  |

| Fixed oxide charge density                            | $Q_f$                | $10^{11}$            | cm <sup>-2</sup> |  |

| Relative dielectric constant of the insulator         | $\varepsilon_{r,ox}$ | 3.9-30               | -                |  |

| Relative dielectric constant of Si                    | $\varepsilon_{r,Si}$ | 11.8                 | -                |  |

Dielectric constant/permittivity is the characteristic of a material. It is defined as the amount of electric flux traversing through a particular material as compared to the vacuum of free space. This material is used as the gate insulation material for various types of MOS devices. Table II shows some widely used gate insulation materials for the MOS devices and their corresponding dielectric constants. In this work, we will use these materials to observe their impact on various operational parameters of the pocket implanted n-MOS devices. Table II shows relative dielectric constants of various gate insulator materials used in this structure.

TABLE II

GATE INSULATION MATERIALS AND THEIR DIELECTRIC CONSTANTS [17]

| Material Name     | Molecular Formula  | Dielectric Constant |

|-------------------|--------------------|---------------------|

| Silicon dioxide   | SiO <sub>2</sub>   | 3.9                 |

| Aluminum silicate | $Al_2SiO_5$        | 5.5                 |

| Silicon nitride   | $Si_3N_4$          | 7.0                 |

| Aluminum oxide    | $Al_2O_3$          | 9.0                 |

| Hafnium silicate  | HfSiO <sub>4</sub> | 11.0                |

| Tantalum oxide    | $Ta_2O_5$          | 22.0                |

| Hafnium oxide     | $HfO_2$            | 25.0                |

| Zirconium Hafnium | $ZrO_2$            | 26.0                |

| Lanthanum oxide   | $La_2O_3$          | 30.0                |

#### III. POCKET DOPED MOS DEVICE MODELS

Device models are developed under some contextual situations to allow the device engineers to inspect the functionality of the designed device to diverse input signals before manufacturing it in real-time. Moreover, such type of model affords the device engineers to have a greater intuition of the device's performance. As such, any kind of MOS device modeling begins from an elementary theoretical concept focusing on the dominant phenomena and then transforming them into a set of mathematical expressions. These models are also called the analytical models. There are certain types of typical trade-offs among generality, accuracy, development cost, and execution speed for such types of MOS transistor models. There are already several models for the pocket implanted MOS transistors to test the effect on the variation of the device dimensions and parameters. These models are useful for the device design engineers or the process engineers to estimate the device performance due to the horizontal doping distribution in an n-MOSFET demonstrating RSCE.

The derived models of the pocket implanted MOS

transistors in the next sub-sections allow us to compute the impacts on the various operating parameters of this device due to the variation of the gate insulation thickness and materials. The models used in this work assume to have the shape of a straight line for the pocket doping concentration profile. The straight-line equations employed to define this shape were specified in [12]. Using those equations, an effective doping concentration equation was derived to use in various models of pocket implanted MOS device as shown in (1):

$$N_{eff} = N_{sub} \left( 1 - \frac{L_p}{L} \right) + \frac{N_{pm}L_p}{L} \tag{1}$$

Some important parameters that are used in this thesis for modeling the pocket implanted n-MOSFET are presented in Table III. The model parameters are briefly described in the next sub-sections.

TABLE III List of the Model Parameters Studied in This Work [10]

| Name of the Model Parameter | Symbol of the Model | Unit                 |

|-----------------------------|---------------------|----------------------|

| Threshold Voltage           | $V_{\it th}$        | V                    |

| Surface Potential           | $\psi_s$            | V                    |

| Inversion Layer Charge      | $Q_{inv}$           | C/cm <sup>2</sup>    |

| Pinch Off Voltage           | $V_p$               | V                    |

| Effective Mobility          | $\mu_{e\!f\!f}$     | cm <sup>2</sup> /V.s |

| Subthreshold drain current  | $I_{d,sub}$         | A                    |

#### A. Threshold Voltage Model

In [10], the threshold voltages ( $V_{th}$ ) model was derived by solving the 1-D Poisson equation with the application of Gauss's law incorporating the substrate and drains biases effect and the pocket implantation doping concentration profile along the channel and is demonstrated in (2):

$$V_{th} = V_{th,L} + \gamma_B \sqrt{\left[\frac{N_{sub}}{N_{eff}}(2\varphi_F) - V_{BS}\right]} - \gamma_A \frac{N_{sub}}{N_{eff}} \sqrt{\left[(2\varphi_F)\right]} - \frac{6t_{ox}}{d_1} \left[2(\varphi_{bi} - V_{BS}) + V_{DS}\right] \exp\left(-\frac{\pi L}{4d_1}\right)$$

(2)

where all the parameters are given in [10].

#### B. Surface Potential Model

When gate bias is applied to an n-MOSFET, a negatively charged depletion region is created near the surface up to a point in the bulk after which the substrate is neutral. The surface potential ( $\psi_s$ ) is defined as the potential drop across the depletion region. By applying Gauss's law and solving the  $2^{nd}$  differential equation with appropriate boundary conditions, the desired analytical surface potential model is obtained as given in (3) [20]:

$$\psi_{s}(x) = \frac{c_{1}}{\sinh\sqrt{\frac{a_{0}}{a_{2}}}L}\sinh\sqrt{\frac{a_{0}}{a_{2}}}(L-x) + \frac{c_{1}+V_{DS}}{\sinh\sqrt{\frac{a_{0}}{a_{2}}}L}\sinh\sqrt{\frac{a_{0}}{a_{2}}}x - \frac{b_{1}}{a_{0}}$$

(3)

where all the parameters are given in [20].

#### C. Inversion Layer Charge Model

The inversion layer charge model derived by incorporating the surface potential [8] and threshold voltage [9] models for the pocket implanted n-MOSFET is given in (4) [21]:

$$Q_{inv} = -\sqrt{2q\varepsilon_{Si}N_{eff}}\left[\sqrt{\psi_s + \phi_{th} \exp\left(\frac{\psi_s - 2\varphi_F - V_{DS}}{\phi_{th}}\right)} - \sqrt{\psi_s}\right]$$

(4)

## D. Pinch-Off Voltage Model

The pinch-off voltage  $(V_P)$  is called that minimum drain-to-source voltage at which the surface inversion charge  $(Q_{inv})$  goes down to zero. Therefore, from (4), this model is derived as presented in (5) [21]:

$$V_P = V_{GS} - V_{th} - \gamma_A \left[ \sqrt{V_{GS} - V_{th} + \left(\sqrt{2\varphi_F} + \frac{\gamma_A}{2}\right)^2} - \left(\sqrt{2\varphi_F} + \frac{\gamma_A}{2}\right) \right]$$

(5)

## E. Effective Mobility Model

The effective vertical electric field model is given in (6) [22]:

$$E_{eff} = \frac{c_{ox}}{\varepsilon_{cs}} \left[ \eta (V_{GS} - V_{th}) + V_{th} - V_{FB} - 4\varphi_F \right] \tag{6}$$

Then the effective electron mobility model is derived based on Coulomb, phonon, and surface roughness scattering models and then finally including the ballistic mobility model as given in (7) [22]:

$$\frac{1}{\mu_{n,eff}} = \frac{1}{\mu_{eqv}} + \frac{1}{\mu_{bal}} \tag{7}$$

## F. Subthreshold Drain Current Model

The sub-threshold electron current density from the drain to source terminals is given by (8) [23]:

$$J_n = -q D_n N_{eff} \exp\left(-\frac{\varphi_{bi} - V_{BS}}{\phi_{th}}\right) \frac{\left\{1 - \exp\left(\frac{V_{DS}}{\phi_{th}}\right)\right\}}{\int_0^L \exp\left(-\frac{\psi_{S}}{\phi_{th}}\right) dx}$$

(8)

## IV. RESULTS AND DISCUSSIONS

This section explores the impact of gate oxide thickness and gate insulation material variation on different model parameters of the pocket implanted n-MOSFET developed

earlier [8]-[10], [20]-[23] through different simulation results for the various device and pocket profile parameters as well as different bias conditions. For simulation purposes, the MATLAB software package of version 2018 is used. Codes have been developed in the MATLAB environment for all the models developed. Pocket profiles are also simulated using MATLAB codes. MATLAB simulation of all the codes has been performed in HP laptop having 1 TB hard disk drive, 512 GB SSD, 8 GB RAM, and an Intel Corei5 processor with a processing speed of 3.4 GHz clock frequency in Microsoft Windows 10 operating system. In the following sub-sections, various simulation results are shown.

#### A. Impact on Threshold Voltage

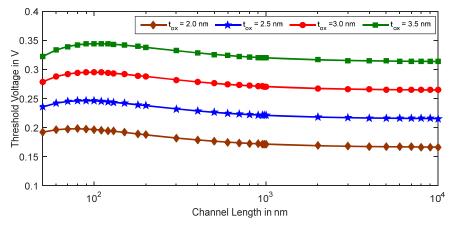

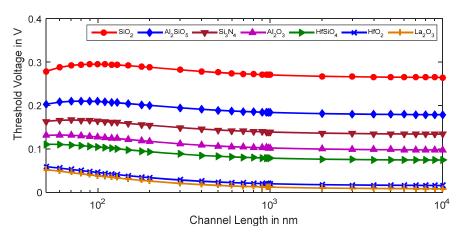

Fig. 2 shows the variation of threshold voltage with the variation of oxide thickness. We observe that as the gate oxide thickness is decreased threshold voltage is reduced. However, in all cases, RSCE is maintained. After that, we have simulated the same model for different gate insulation materials. Their relative dielectric permittivity increases from 3.9 for SiO<sub>2</sub> to 30 for La<sub>2</sub>O<sub>3</sub>. As the dielectric permittivity of the material increases threshold voltages are scaled down for the nano-scaled devices as shown in Fig. 3; because we can accumulate now more flux and charge.

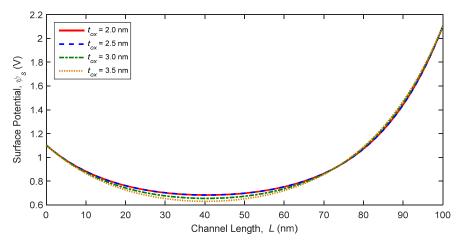

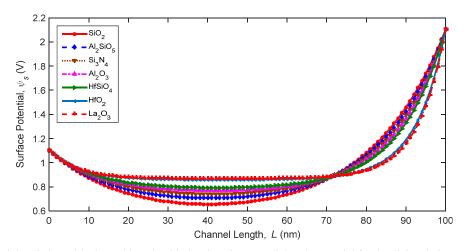

## B. Impact on Surface Potential

Fig. 4 shows the variation of surface potential with the variation of oxide thickness along the channel. We observe that as the gate oxide thickness is decreased surface potential is not changed appreciably. After that, we have simulated the same model for different gate insulation materials. Their relative dielectric permittivity increases from 3.9 for SiO<sub>2</sub> to 30 for La<sub>2</sub>O<sub>3</sub>. As the dielectric permittivity of the material increases, we observe a peculiar behavior at the center and the drain side of the device as shown in Fig. 5. At the central part of the device, we see that as we increase the dielectric constant, the surface potential increases but at the drain side it becomes the opposite.

Fig. 2 Threshold voltage variation with channel length with the changing gate insulation layer thickness for SiO2 as the gate dielectric material

Fig. 3 Threshold voltage variation with channel length with the changing gate insulation materials for the dielectric layer thickness of 3.0 nm

Fig. 4 Surface potential variation with channel length with the changing gate dielectric layer thickness for SiO<sub>2</sub> as the gate dielectric material

Fig. 5 Surface potential variation with channel length with the changing gate dielectric material for the dielectric layer thickness of 3.0 nm

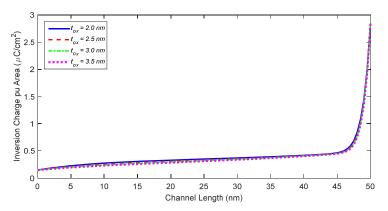

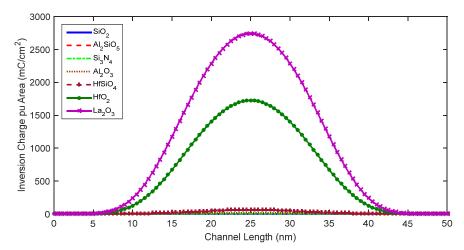

## C. Impact on Inversion Layer Charge

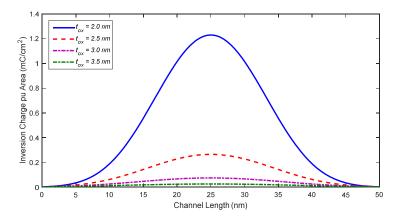

Fig. 6 shows the variation of inversion layer charge per unit area with the variation of oxide thickness along the channel. We observe that as the gate oxide thickness is decreased inversion layer charge is not changed appreciably when both drain and gate voltages are applied. However, in the central part, the inversion layer charge increases with the decrement

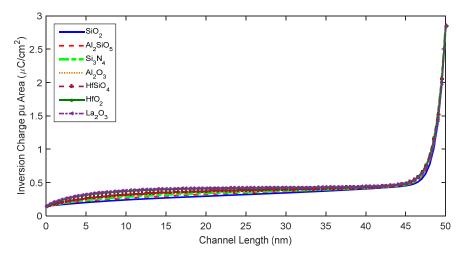

of oxide thickness when the drain voltage is zero but gate voltage is above threshold voltage as shown in Fig. 7. After that, we have simulated the same model for different gate insulation materials. Their relative dielectric permittivity increases from 3.9 for SiO<sub>2</sub> to 30 for La<sub>2</sub>O<sub>3</sub>. As the dielectric permittivity of the material increases, we observe a peculiar behavior at the center and the drain side of the device as

shown in Fig. 8. At the central part of the device, we see that as we increase the dielectric constant, the surface potential increases but at the drain side it becomes the opposite. But this effect is very negligible. However, in the central part, the

inversion layer charge increases with the increment of the oxide layer's dielectric constant when the drain voltage is zero but gate voltage is above threshold voltage as shown in Fig. 9.

Fig. 6 Inversion layer charge variation with channel length with the changing gate dielectric layer thickness for SiO<sub>2</sub> as the gate dielectric material  $V_{DS} = 1.0 \text{ V}$  and  $V_{GS} = 1.0 \text{ V}$

Fig. 7 Inversion layer charge variation with channel length with the changing gate dielectric layer thickness for SiO<sub>2</sub> as the gate dielectric material  $V_{DS} = 0.0 \text{ V}$  and  $V_{GS} = 1.0 \text{ V}$

Fig. 8 Inversion layer charge variation with channel length with the changing gate dielectric material for the dielectric layer thickness of 3.0 nm  $V_{DS} = 1.0 \text{ V}$  and  $V_{GS} = 1.0 \text{ V}$

Fig. 9 Inversion layer charge variation with channel length with the changing gate dielectric material for the dielectric layer thickness of 3.0 nm  $V_{DS} = 0.0 \text{ V}$  and  $V_{GS} = 1.0 \text{ V}$

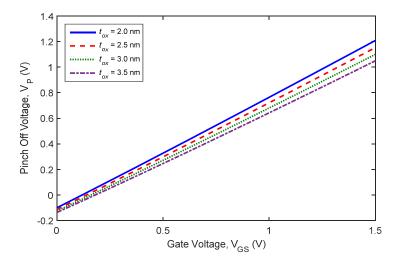

Fig. 10 Pinch-off voltage variation with gate voltage with the changing gate dielectric layer thickness for SiO<sub>2</sub> as the gate dielectric material for  $V_{DS} = 0.0 \text{ V}$  and channel length, L = 50 nm

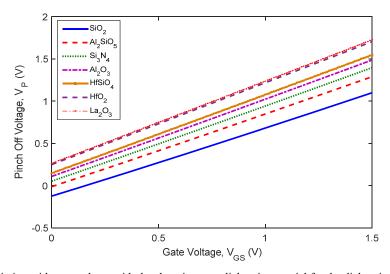

Fig. 11 Pinch-off voltage variation with gate voltage with the changing gate dielectric material for the dielectric layer thickness of 3.0 nm for  $V_{DS} = 0.0 \text{ V}$  and channel length, L = 50 nm

# D.Impact on Pinch Off Voltage

Fig. 10 shows the variation of pinch-off voltage with the variation of oxide thickness versus gate voltage. We observe that as the gate oxide thickness is decreased pinch-off voltage is increased slightly at lower values of gate voltage but it increases greatly if higher values of gate voltage are applied. This phenomenon is observed due to the less amount of inversion charge  $(Q_{inv})$  at a higher thickness of the gate insulating layer as shown in Fig. 7. After that, we have simulated the same model for different gate insulation materials. Their relative dielectric permittivity increases from 3.9 for SiO<sub>2</sub> to 30 for La<sub>2</sub>O<sub>3</sub>. As the dielectric permittivity of the material increases, we observe that as we increase the dielectric constant by changing the gate insulation materials, the pinch-off voltage increases slightly at lower values of gate voltage but it increases greatly if higher values of gate voltage are applied as shown in Fig. 11. This happens due to the increment of inversion layer charge at the surface with the increment of the dielectric permittivity as per Fig. 9. Therefore, we need a higher amount of gate voltage to replenish this charge and also a higher amount of drain voltage to cease the inversion channel at the drain wing of the device.

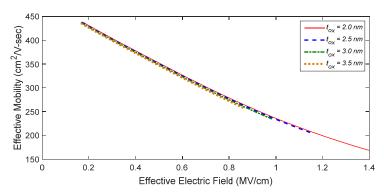

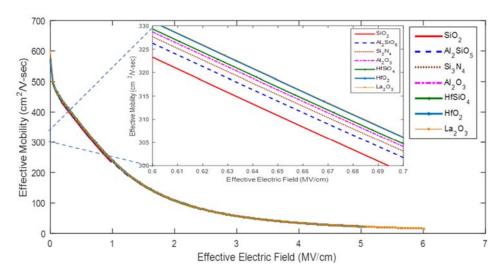

# E. Impact on Effective Mobility

Fig. 12 shows the variation of effective electron mobility with the variation of oxide thickness versus effective vertical gate electric field. We can have more electric fields if we decrease the oxide thickness or increase the dielectric permittivity of the gate insulation material.

Fig. 13 shows the variation of effective electron mobility with the variation of gate insulation materials versus effective vertical gate electric field. As the gate insulation materials are changed their relative dielectric permittivity increases from 3.9 for SiO<sub>2</sub> to 30 for La<sub>2</sub>O<sub>3</sub>. As the gate oxide thickness or the dielectric permittivity of the gate material is changed, we observe a little change in the effective electron mobility in Figs. 12 and 13. However, if we look at the linear portion of the curve of Fig. 13 as shown on the inset figure, we see that the effective mobility goes up with the increment of dielectric strength. Besides, the effective vertical gate electric field increases as we increase the dielectric constant by changing the gate oxide thickness or the gate insulation materials. As such, we observe a slight increment of the electron effective mobility along the channel of the device.

Fig. 12 Effective mobility variation with effective electric field with the changing gate dielectric layer thickness for SiO<sub>2</sub> as the gate dielectric material

Fig. 13 Effective mobility variation with effective electric field with the changing gate dielectric materials for the dielectric layer thickness of 3.0 nm

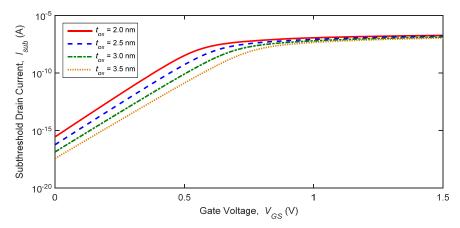

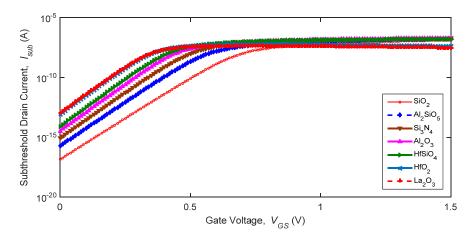

# F. Impact on Subthreshold Drain Current

Fig. 14 shows the variation of subthreshold drain current with the variation of gate insulation layer thickness versus gate voltage. We observe that as the gate oxide thickness is decreased subthreshold drain current is increased for a particular gate voltage but it increases slightly if higher values of gate voltage are applied.

Fig. 15 shows the variation of subthreshold drain current with the variation of gate insulation materials versus gate

voltage. As the gate insulation materials are changed, their relative dielectric permittivity increases from 3.9 for SiO<sub>2</sub> to 30 for La<sub>2</sub>O<sub>3</sub>. As the dielectric permittivity of the material is raised, we observe that subthreshold drain current is increased for a particular gate voltage but it increases slightly if higher values of gate voltage are applied. However, for the higher gate voltage, this phenomenon reverses as we increase the dielectric constant by changing the gate insulation materials as it happened in the case of the surface potential model.

Fig. 14 Subthreshold drain current variation with gate voltage with the changing gate dielectric layer thickness for SiO<sub>2</sub> as the gate dielectric material

Fig. 15 Subthreshold drain current variation with gate voltage with the changing gate dielectric material for the dielectric layer thickness of 3.0 nm

### V. CONCLUSION

When the thickness of the gate insulating layer decreases beyond 2 nm, the leakage current upsurges significantly due to the electron tunneling process through this layer. As a result, we need to substitute the gate dielectric material, for example, SiO<sub>2</sub> with a substantially wider insulating layer having high-k dielectric, such as Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, etc. These materials permit the capacitance to rise without raising the leakage current much. Therefore, in this work, different models of the pocket implanted nano-scaled n-MOSFET have been simulated in MATLAB for various values of the gate insulation layer thickness and gate insulation materials having

high-k dielectric. From the simulation results, we can conclude that in the nano-scaled pocket implanted MOS devices, the lower values of gate insulation layer thickness and gate insulation materials with the higher values of dielectric permittivity (i.e., with high-k dielectric materials) should be utilized to get the optimum device performance.

#### REFERENCES

- [1] A. Hokazono, S. Balasubramanian, K. Ishimaru, H. Ishiuchi, H. Chenming and L. T.-J. King, "MOSFET hot-carrier reliability improvement by forward-body bias," IEEE Electron Device Letters, vol. 27, no. 7, pp. 605-608, July 2006.

- [2] B. Yu, C. H. Wann, E. D. Nowak, K. Noda and C. Hu, "Short Channel Effect improved by lateral channel engineering in deep-submicrometer

- MOSFETs," IEEE Transactions on Electron Devices, vol. 44, pp. 627-633, Apr. 1997.

- [3] B. Yu, H. Wang, O. Millic, Q. Xiang, W. Wang, J. X. An and M. R. Lin, "50 nm gate length CMOS transistor with super-halo: Design, process and reliability," IEEE IEDM Technical Digest, pp. 653-656, 1999.

- [4] Y. S. Pang and J. R. Brews, "Models for subthreshold and above subthreshold currents in 0.1

m pocket n-MOSFETs for low voltage applications," IEEE Transactions on Electron Devices, vol. 49, no. 5, pp. 832-839, May 2002.

- [5] M. K. Khanna, M. C. Thomas, R. S. Gupta and S. Haldar, "An analytical model for anomalous threshold voltage behavior of short-channel MOSFETs," Solid-State Electronics, vol. 41, pp. 1386-1388, 1997.

- [6] H. Brut, A. Juge, and G. Ghibaudo, "Physical model of threshold voltage in silicon MOS transistors including reverse short channel effect," Electronics Letters, vol. 31, no. 5, pp. 410-12, March 1995.

- [7] M. H. Bhuyan and Q. D. M. Khosru, "Low-Frequency Drain Current Flicker Noise Model for Pocket Implanted Nano Scale n-MOSFET," Proceedings of the IEEE and EDS sponsored Nano Materials and Device Conference (NMDC), 12-15 October 2010, CA, USA, pp. 295-299.

- [8] M. H. Bhuyan and Q. D. M. Khosru, "An analytical surface potential model for pocket implanted sub-100 nm n-MOSFET," Proceedings of the 5<sup>th</sup> IEEE International Conference on Electrical and Computer Engineering, Dhaka, 20-22 December 2008, pp 442-446.

- [9] M. H. Bhuyan and Q. D. M. Khosru, "Linear pocket profile based threshold voltage model for sub-100 nm n-MOSFET," International Journal of Electrical and Computer Engineering, vol. 5, no. 5, pp. 310-315, May 2010.

- [10] M. H. Bhuyan, "Analytical modeling of the pocket implanted nanoscale n-MOSFET," PhD Thesis, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, 2011.

- [11] M. H. Bhuyan and Q. D. M. Khosru, "An analytical subthreshold drain current model for pocket implanted nanoscale n-MOSFET," Journal of Electron Devices, ISSN 1682-3427, vol. 8, pp 263-267, October 2010.

- [12] M. H. Bhuyan, F. Ferdous and Q. D. M. Khosru, "A threshold voltage model for sub-100 nm pocket implanted NMOSFET," Proceedings of the 4<sup>th</sup> IEEE International Conference on Electrical and Computer Engineering, Dhaka, Bangladesh, 19-21 December 2006, pp. 522-525.

- [13] X. Zhou, K. Y. Lim and D. Lim, "Physics-Based threshold voltage modeling with Reverse Short Channel Effect," Journal of Modeling and Simulation of Microsystems, Vol. 2, No. 1, pp. 51-56, 1999.

- [14] X. Zhou, K. Y. Lim and D. Lim, "A general approach to compact threshold voltage formulation based on 2-D numerical simulation and experimental correlation for deep-submicron ULSI technology development," IEEE Trans. on Electron Devices, vol. 47, no. 1, pp. 214-221, Jan. 2000.

- [15] A. Mondal, A. Roy, R. Mitra and A. Kundu, "Comparative Study of Variations in Gate Oxide Material of a Novel Underlap DG MOS-HEMT for Analog/RF and High Power Applications," Silicon, Springer, vol. 12, pp. 2251–2257, 2020.

- [16] A. A. Sayem, Y. Arafat and M. M. Rahman, "Effect of High k-Dielectric as Gate Oxide on Short Channel Effects of Junction-less Transistor," Proceedings of the 2<sup>nd</sup> IEEE International Conference on Advances in Electrical Engineering (ICAEE 2013), 19-21 December 2013, Dhaka, Bangladesh, pp. 115-118.

- [17] J. Robertson and R. M. Wallace, "High-K materials and metal gates for CMOS applications," Journal of Materials Science and Engineering R, vol. 88, 2015, pp. 1-41.

- [18] G. Sethi, M. Olszta, J. Li, J. Sloppy, M. W. Horn, E. C. Dickey and M. T. Lanagan, "Structure and dielectric properties of amorphous tantalum pentoxide thin film capacitors," 2007 Annual Report Conference on Electrical Insulation and Dielectric Phenomena, pp. 815-818.

- [19] K. Koley, A. Dutta, B. Syamal, S. K. Saha, C. K. Sarkar, "Subthreshold analog/RF performance enhancement of underlap DG FETs with high-k spacer for low power applications," IEEE Transaction on Electron Devices, vol. 60, no. 1, pp, 63-69, 2013.

- [20] M. H. Bhuyan and Q. D. M. Khosru, "Linear Profile Based Analytical Surface Potential Model for Pocket Implanted Sub-100 nm n-MOSFET," Journal of Electron Devices, France, 1682-3427, vol. 7, April 2010, pp 235-240.

- [21] M. H. Bhuyan and Q. D. M. Khosru, "Linear Pocket Profile Based Pinch Off Voltage Model for Nanoscale n-MOSFET," Proceedings of the 2<sup>nd</sup> IEEE International Conference on Electrical, Computer and Telecommunication Engineering (ICECTE 2016), Rajshahi University of Engineering and Technology (RUET), Rajshahi, Bangladesh, 8-10

- December 2016, pp. 1-4, doi: 10.1109/ICECTE.2016.7879624.

- [22] M. H. Bhuyan and Q. D. M. Khosru, "Inversion Layer Effective Mobility Model for Pocket Implanted Nano Scale n-MOSFET," International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, ISSN: p:2010-376X, e:2010-3778, vol. 5, no. 1, 2011, pp. 1-8.

- [23] M. H. Bhuyan and Q. D. M. Khosru, "Analytical Subthreshold Drain Current Model Incorporating Inversion Layer Effective Mobility Model for Pocket Implanted Nano Scale n-MOSFET," International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, ISSN: p: 2010-376X, e: 2010-3778 vol. 7, no. 4, 2013, pp. 465 - 472.

Muhibul Haque Bhuyan (MIEEE'07—) became a Member (M) of World Academy of Science, Engineering and Technology in 2005, born in Dhaka, Bangladesh on 25 July. He did his BSc, MSc, and PhD degrees in Electrical and Electronic Engineering (EEE) from Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh in 1998, 2002, and 2011 respectively.

Currently, he is working as a Professor of the Department of Electrical and Electronic Engineering of Southeast University, Dhaka, Bangladesh. He led this department as the Departmental Chairman from 1st March 2016 to 10 March 2021. Previously, he worked at the Green University of Bangladesh, Dhaka as a Professor and Chairman of the EEE Department; Daffodil International University, Dhaka, Bangladesh as an Assistant Professor and Head of ETE Department; Presidency University, Dhaka, Bangladesh as an Assistant Professor and American International University Bangladesh (AIUB), Dhaka as a Faculty Member since June 1999. He also worked as a Researcher in the Center of Excellence Program of Hiroshima University, Japan from July 2003 to March 2004. So far, he has published over 40 research papers in national and international journals and presented over 50 research works at national and international conferences. His research interests include MOS device modeling, biomedical engineering, control system design, outcome-based engineering education, assessment, and evaluation.

Prof. Bhuyan is a Member of IEEE, USA, Executive Member of Bangladesh Electronics and Informatics Society (BEIS), and Fellow of the Institution of Engineers Bangladesh (IEB). He is a regular reviewer and technical/editorial/organizing committee member of several national and international journals and conferences. He was the Organizing Chair of the recently held IEEE 22nd International Conference on Computer and Information Technology (ICCIT) in Dhaka, Bangladesh during 18-20 December 2019. He is the recipient of the Bangladesh Education Leadership Awards (Best Professor in Electrical Engineering) in 2017 from the South Asian Partnership Awards, Mumbai, India.